TI高性能模拟器件选型指南——ADC和DAC

-

ADC和DAC

1. ADC

-

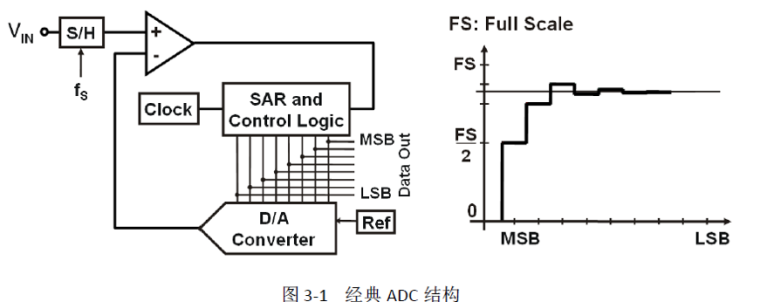

ADC的基本原理

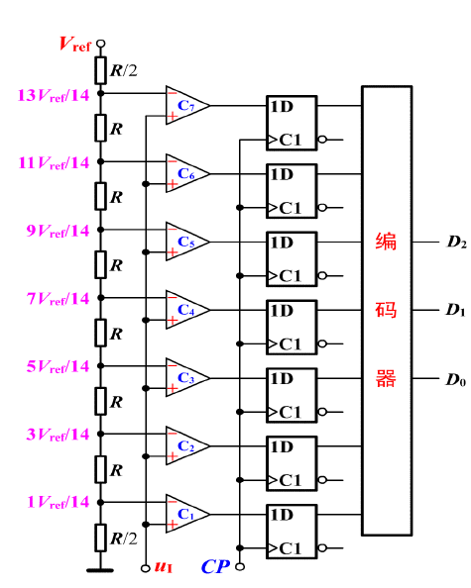

如图所示的ADC称之为Flash ADC,也叫并行ADC的基本结构,对于n位输出的二进制码,需要2n-1个比较器。

-

ADC的基本分类:

除了并行ADC外,常用的ADC还有

- 逐次逼近型(SAR型)

- 流水线型(Pipeline型)

- 插值结构和折叠插值型

- Σ-Δ型

-

量化误差与分辨率:

-

ADC 转换包括采样、保持、量化、编码4 个步骤。其中,量化是指将信号的连续取值近似为有限多个离散值的过程。对于多bit的ADC,量化误差一般在 ±1/2 LSB。

-

满量程输入范围叫FW , 输入的位数叫分辨率

-

-

过采样和欠采样

- 采样频率fs应大于或等于模拟信号频率的两倍,满足香农采样定律。当fs>2fh时,称为过采样;fs<2fh时,称为欠采样,欠采样过程中发生的频率偏移叫做混叠。

2. ADC的性能指标:

-

静态精度:

静态精度由静态误差反应。静态误差可以由偏置误差,增益误差,积分非线性误差以及微分非线性误差来描述。

-

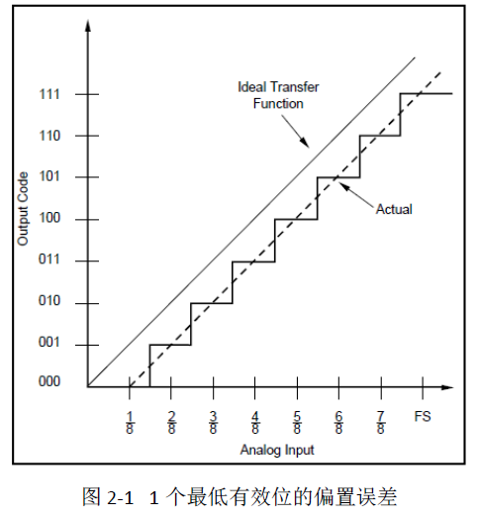

偏置误差:

如图是偏置误差为1 位最低有效位的3 位A/D 转换器转换特性图,偏置误差为当输入等于0.5 个最低有效位时,第一个码字转换(从000 到001)偏离理想位置的值。

-

增益误差: 增益误差可以描述为直线通过转换函数曲线时,在满量程处的偏差。

-

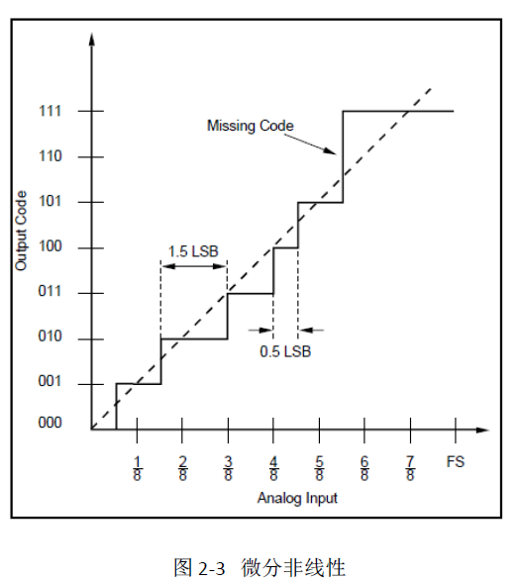

微分非线性:

微分非线性通常用来描述在转换过程中发生码字跳转处的输入电压偏 离理想转换电压的大小。

-

积分非线性误差:

-

动态指标:

-

无杂波动态范围(SFDR)

-

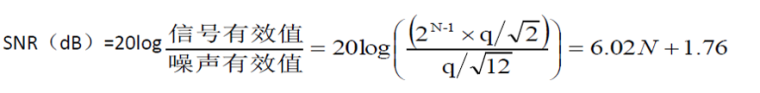

信噪比(SNR):

SNR指的是信号有效值和噪声有效值之比

-

3.ADC选型指南:

-

SAR型ADC

SAR型ADC是一种逐次逼近的类型,例如一个6位的ADC,会先让输入比较32, 再比较32±16,逐渐逼近。它具有简单易用,功耗低的优点,但是缺点是转换时间过长。

-

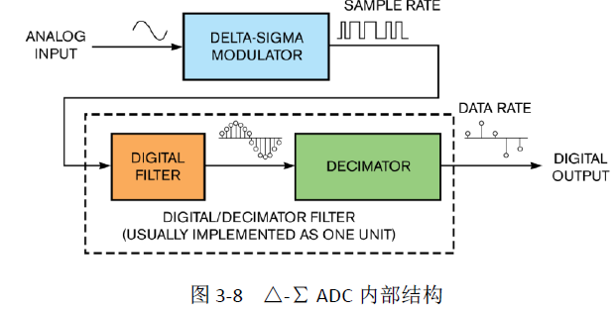

△-Σ ADC:

其核心部分是一个△-Σ 调制器级联一个数字滤波器。

-

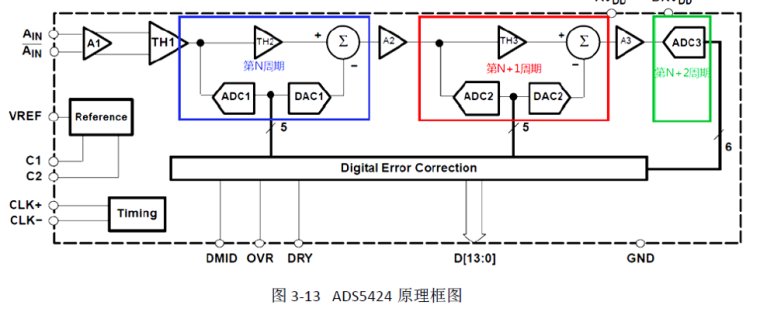

流水线型ADC(Pipeline):

如图所示, ADC有3级流水线,其中ADC1是Flash结构,因此可以同时达到高速度和高精度。

-

-

ADC的选取:

- 确定ADC的类型:SAR、Δ Σ、Pipelined

- 确定所需ADC 的采样率,精度

- 选择并设计ADC 的模拟输入:根据 ADC的模拟输入端是单端输入还是差分输入,信号的通道数、信号的极性和大小

- 选择ADC的参考输入

- 确定ADC的数据输出捕获:SPI或I2C

4.DAC简介和性能指标:

- DAC性能指标:

- 偏置误差: 偏置点为数字输入为零时的步长值

- 增益误差: 偏置误差调整为零后,DAC 数字输入量为满量程时,实际的

输出值和理论值之间的误差。 - 分辨率:能分辨的最小模拟输出量

- 输出电压

- 转换时间

5.DAC选型和指南:

-

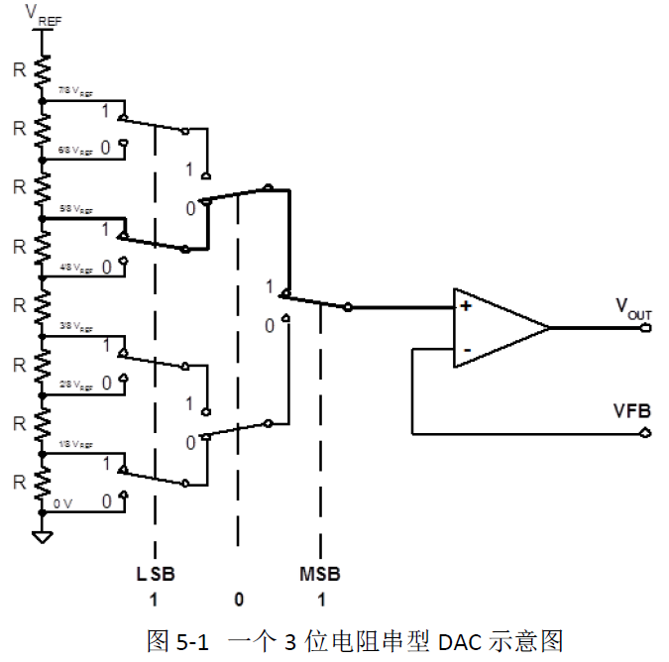

常见DAC结构与应用场景:常见DAC结构可分为通用型(R-string)和双极型(MDAC)

- 电阻串型DAC(R-String):

采用模拟开关加电阻串的方式对参考输入电压分压,再通过运放缓冲分压结果输出。需要的电阻较多,精度也很难做得很高。因此,在12 位及以上的DAC 中,通常采用2 级R String 的方式来减少电阻器的数量。

-

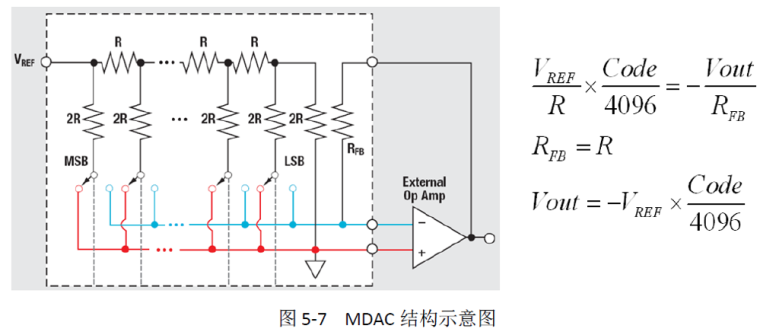

乘法型DAC R-2R:

-

Δ Σ 型DAC: 采用delta-sigma 技术以提高转换的精度,一般用于音频DAC。

-

电流引导型DAC Current Steering: 是一种高速DAC, 基于亚微米CMOS或BiCMOS的工艺, 实现了1GSPS的刷新率以及14位,甚至16位的分辨率

-

PWM DAC: 采用PWM调控来实现DAC变换,通常应用在嵌入式设备中。

-

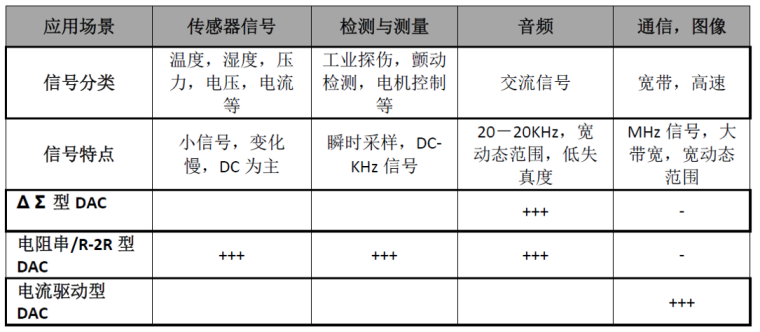

DAC应用场景总结: 根据不同DAC 性能的特点,在不同的应用场合应选择不同的DAC

- 电阻串型DAC(R-String):

-

DAC选型与电路设计:

- 确定所需DAC的类型

- 确定所需的分辨率和建立时间

- 选择并设计DAC的模拟输出端

- 选择并设计DAC 的参考电压输入端

- 选择设计高速DAC的时钟

- DAC的数据输入: SPI或I2C

6.低噪声电路的设计与优化

-

精密信号链中的噪声抑制:

-

噪声来源:

器件噪声:板上所有的有源或无源器件都会带来器件噪声。

辐射噪声:该类噪声通常来自相邻数字信号走线或周围环境

传导噪声: 传导噪声可以由辐射噪声或器件噪声产生。

-

减少器件噪声: 增加去偶电容

-

减少辐射噪声: 避免环形走线和长走线

-

-