学习笔记(四)

-

学习笔记五

一、 ADC噪声系数(NF)

1. ADC噪声系数定义

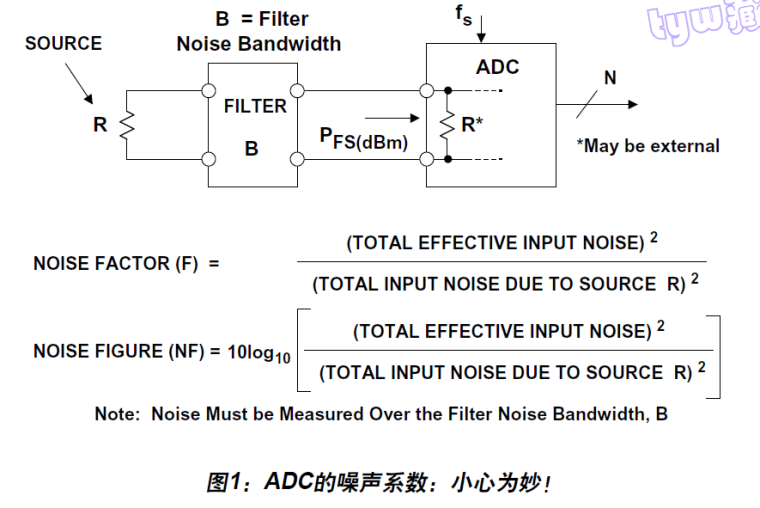

下图显示了用于定义ADC噪声系数的基本模型。噪声因数F指的是ADC的总有效输入噪声功率与源电阻单独引起的噪声功率之比。由于阻抗匹配,因此可以用电压噪声的平方来代替噪声功率。噪声系数NF是用dB表示的噪声因数,NF = 10log10F。

2. 改善噪声系数

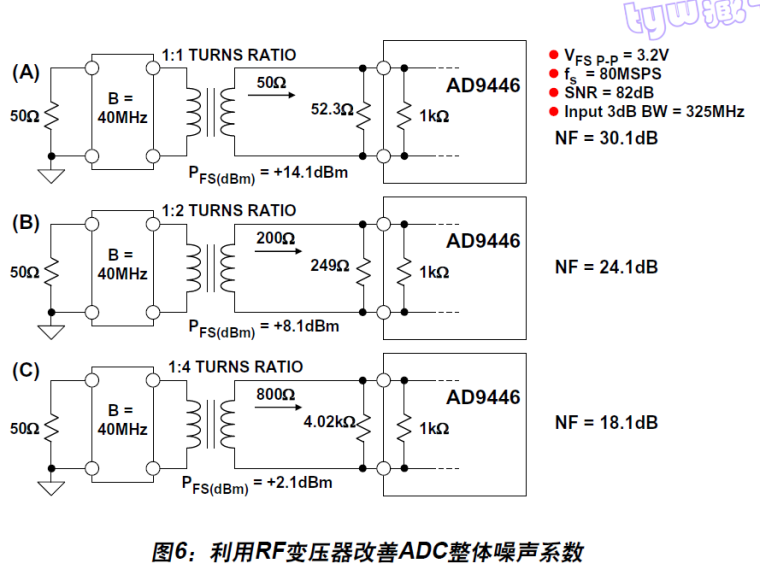

- 利用变压器,理论上,匝数比越高,则改善幅度越大,但由于带宽和失真限制,更高匝数比的变压器一般并不可行。

- 可在ADC前方放置一个低噪声增益模块与ADC级联,将总噪声降低。

二、 ADC架构

1. Flash转换器

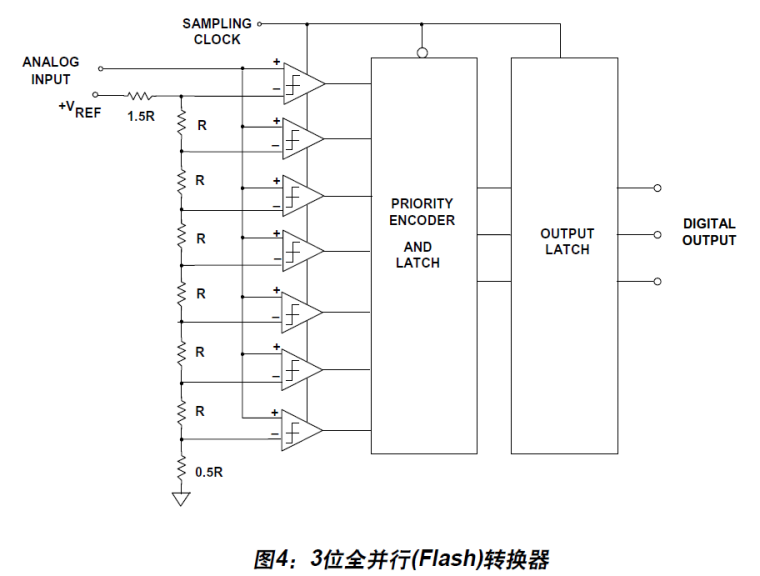

Flash ADC(有时称为“并行”ADC)是速度最快的ADC,一个N位flash ADC包括2N个电阻和2N – 1个比较器。由于flash转换器采用了大量电阻和比较器且限制在低分辨率,因此如果达到较高速度,每个比较器就必须以相对较高的功耗水平运行。因此,flash ADC的问题包括分辨率有限(常被限制为6位或8位)、因使用大量高速比较器(尤其是采样速率超过50 MSPS时)而导致功耗较高和相对较大(因此成本较高)的芯片尺寸。

2. 逐次逼近型ADC(SAR ADC)

CONVERT START命令置位时,采样保持(SHA)电路置于保持模式,而内部DAC设为中间电平。比较器确定SHA输出是大于还是小于DAC输出,并将结果(位1,转换的最高有效位)存储在逐次逼近型寄存器(SAR)中。然后,DAC被设为¼量程或¾量程(取决于位1的值),而比较器则确定转换的位2。结果同样存储在寄存器中,而该过程继续进行,直到确定所有位的值为止。

随着逐次逼近型ADC日益受欢迎,其分辨率、采样速率、输入/输出选项和成本开始出现多样化。现在,很多SAR ADC提供片上输入多路复用器,非常适合多通道数据采集系统。

3.

型ADC

型ADC是现代语音频带、音频和高分辨率精密工业测量应用所青睐的转换器。高度数字架构非常适合现代细线CMOS工艺,因而允许轻松添加数字功能,而又不会显著增加成本。现代CMOS 型ADC(以及DAC,就此而言)是语音频带和音频应用所青睐的转换器。高度数字化架构使得其非常适合细线CMOS工艺。此外,高分辨率(最高达24位)低频 型ADC在精密工业测量应用中几乎已经取代了老的积分型转换器。 4. 计数ADC

计数ADC技术的基本原理是利用一个采样脉冲对模拟信号进行采样,然后设置一个R/S触发器,同时启动一个受控斜坡电压。该斜坡电压与输入进行比较,当二者相等时,就会产生一个脉冲以复位R/S触发器。触发器的输出是一个脉冲,其宽度与采样时刻的模拟信号成正比。该脉宽调制(PWM)脉冲控制一个选通振荡器,选通振荡器输出的脉冲数量代表模拟信号的量化值,通过一个计数器很容易将该脉冲串转换成一个二进制字。计数ADC虽然不太适合高速应用,但却是高分辨率低频应用的理想之选。

三、 ADC输入噪声利与弊

1. 通过数字均值法提高ADC分辨率并降低噪声

折合到输入端噪声的影响可以通过数字均值方法降低。假设一个16位ADC具有15位无噪声分辨率,采样速率为100 kSPS。对于每个输出样本,如果对两个样本进行平均,则有效采样速率降至50 kSPS,SNR提高3 dB,无噪声位数提高到15.5位。如果对四个样本进行平均,则采样速率降至25 kSPS,SNR提高6 dB,无噪声位数提高到16位。通过均值技术提高分辨率时,需要少量的折合到输入端噪声,但如果噪声太高,均值法将需要大量样本,而且存在一个“效益递减”点。

2. 利用噪声扰动提高ADC无杂散动态范围

对于高速ADC,若要最大程度地提高SFDR,存在两个基本限制:第一是前端放大器和采样保持电路产生的失真;第二是ADC编码器部分的实际传递函数的非线性所导致的失真。提高SFDR的关键是尽可能降低以上两种非线性。要显著降低ADC前端引起的固有失真,在ADC外部着力是徒劳的。然而,ADC编码器传递函数的微分非线性可以通过适当利用扰动(即外部噪声,与ADC的模拟输入信号相加)来降低。在一定的条件下,扰动可以改善ADC的SFDR。

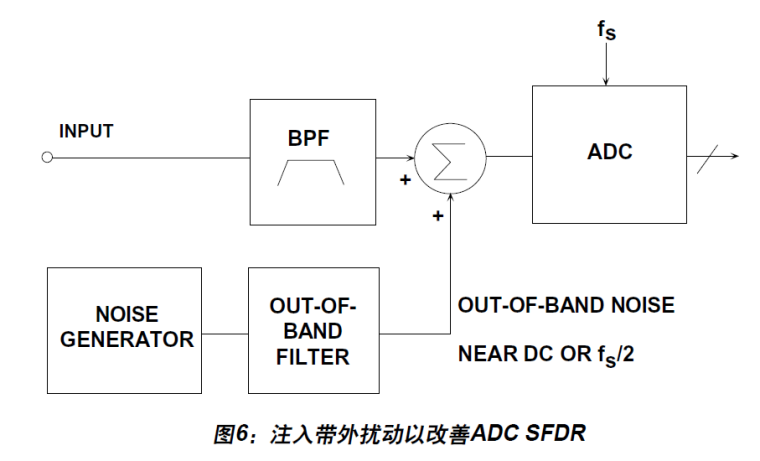

注入信号目标频带以外的一个窄带扰动信号,如下图所示。一般来说,信号成分不会位于接近DC的频率范围,因此该低频区常用于这种扰动信号。扰动信号可能还位于略低于fs/2的地方。相对于信号带宽,扰动信号仅占用很小的带宽(数百kHz带宽通常即足够),因此SNR性能不会像在宽带扰动下那样显著下降。

四、 FPGA与ADC数字数据输出的接口

进行ADC与FPGA的接口设计时,下列一般建议会有所帮助。

- 使用接收器、FPGA或ASIC的外部电阻终端,而不要使用FPGA内部终端,以免不匹配引起反射,致使超出时序预算。

- 如果系统使用多个ADC,请勿使用某个ADC的某个DCO。

- 布设连接到接收器的数字走线时,请勿采用大量“转接”(tromboning)来使所有走线保持等长。

- 利用CMOS输出端的串联终端降低边沿速率并限制开关噪声。确认所用的数据格式(二进制补码或偏移二进制)正确。

五、 噪底

总谐波失真(THD)指的是基波信号的均方根值与其谐波(一般仅前5次谐波比较重要)的和方根的平均值之比。

无杂散动态范围 (SFDR) 指的是信号的均方根值与最差杂散信号(无论它位于频谱中何处)的均方根值之比。它代表了可以与大干扰信号(阻塞信号)相区别的最小信号值。

信纳比(SINAD或S/(N + D))指的是信号幅度均方根与所有其它频谱成分(包括谐波但不含直流)的和方根(rss)的平均值之比。SINAD很好地反映了ADC的整体动态性能,因为它包括所有构成噪声和失真的成分。SINAD曲线常常针对不同的输入幅度和频率而给出。

常常利用理想N位ADC的理论SNR计算公式(SNR = 6.02N + 1.76 dB),将SINAD换算为有效位数(ENOB)。

SINAD、SNR和THD之间存在数学关系。

SINAD = 20log(S/(N+D)) = -10log(10^-SNR/10^+10^-THD/10^)

SNR = 20log(S/N) = -10log(10^-SINAD/10^-10^-THD/10^)

THD = 20log(S/D) = -10log(10^-SINAD/10^-10^-SNR/10^)

六、 将相位噪声转换为时间噪声

用于产生采样时钟的振荡器常常用相位噪声而非时间抖动来描述特性,可用一种简单的方法来将振荡器相位噪声转换为时间抖动。

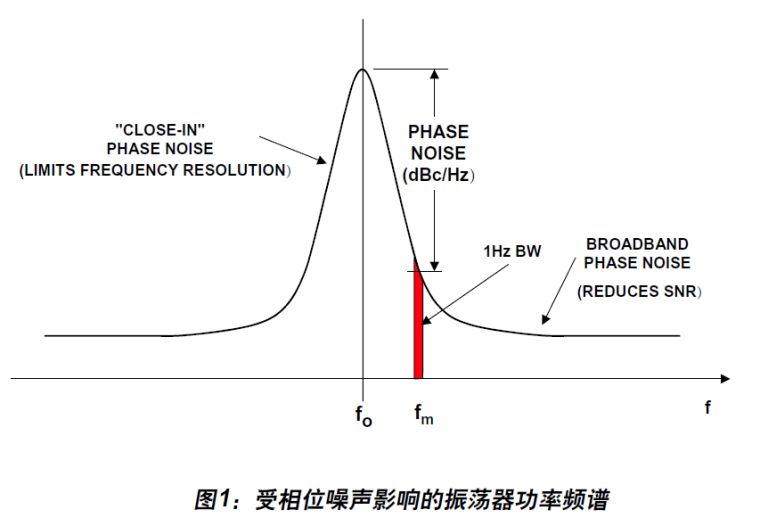

下图所示为一个非理想振荡器(即时域中存在抖动,对应于频域中的相位噪声)的典型输出频谱。频谱显示,1 Hz带宽内的噪声功率与频率成函数关系。相位噪声定义为额定频率偏移f~m~下的1 Hz带宽内的噪声与频率f~O~下的振荡器信号幅度之比。

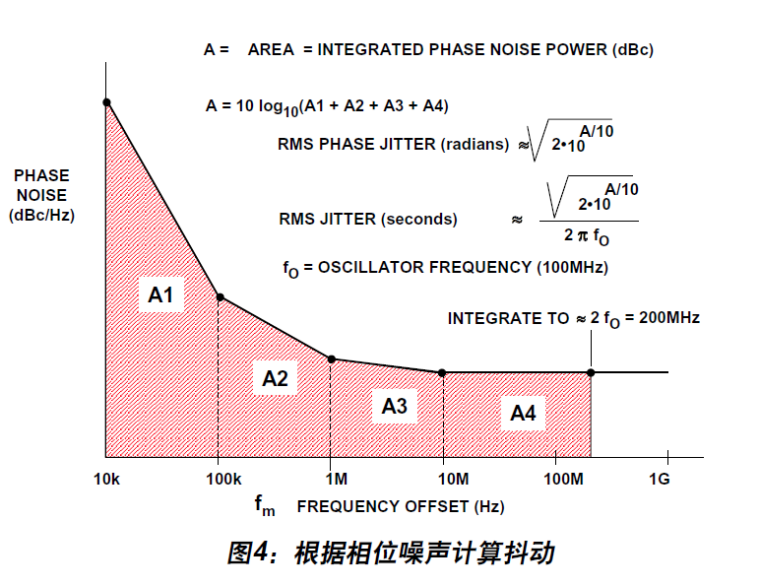

计算等效rms抖动的第一步是获得目标频率范围(即曲线区域A)内的积分相位噪声功率。一旦知道积分相位噪声功率,便可通过下式计算rms相位抖动

七、 旋变数字转换器(RDC)

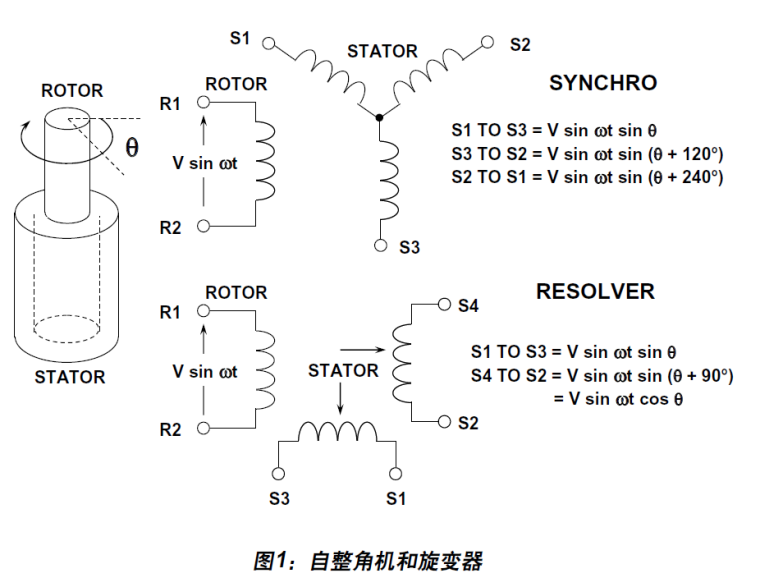

加工工具和机器人制造商利用旋变器和自整角机来提供精确的角度和旋转信息。典型的自整角机和旋变器如下图所示。

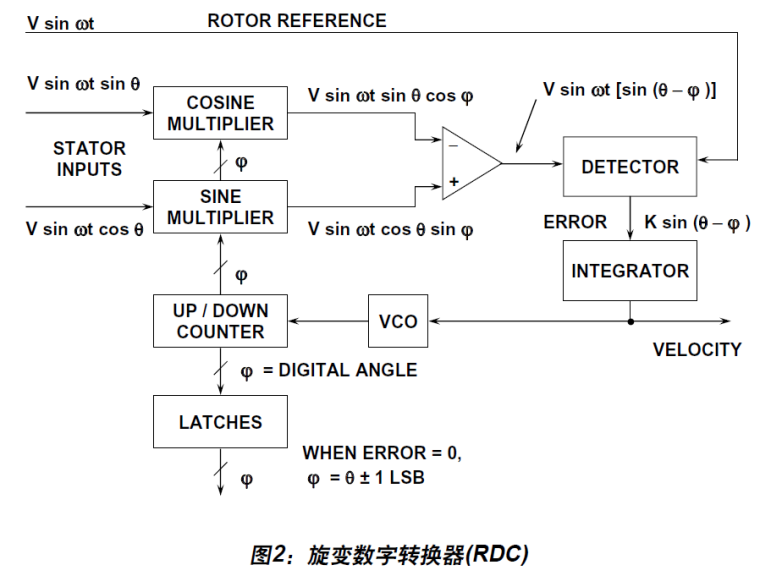

下图所示为典型旋变数字转换器(RDC)的功能框图。

八、 降低ADC时钟接口抖动

时钟接口阈值区间附近的抖动会破坏模数转换器(ADC)的时序。例如,抖动会导致ADC在错误的时间采样,造成对模拟输入的误采样,并且降低器件的信噪比(SNR)。

时钟和ADC之间的电路噪声是时钟抖动的根本原因。随机抖动由随机噪声引起,随机噪声通过其无界字符来区分,遵循统计分布规律。确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。

可使用PLL对参考时钟输出进行滤波,还使用了高质量的VCXO。PLL可以从恢复后的系统时钟去除无用抖动。AD9523、AD9524和AD9523-1时钟发生器在单个器件内集成了抖动清除和时钟产生/分配功能。

九、 高速ADC模拟输入接口考虑

1. 输入接口考虑

-

输入阻抗是设计的特征阻抗。ADC的内部输入阻抗取决于ADC架构的类型,ADC供应商会在数据手册或产品页面上提供这一数据。

-

输入驱动与带宽特性相关,可设置特定应用所需的系统增益。

-

带宽是系统要使用的频率范围。通带平坦度是指定带宽内的波动量;引起波动的原因可能是纹波效应,或者是巴特沃兹滤波器的慢速滚降特性。

-

信噪比(SNR)和失真要求对ADC的选择有帮助,因而一般在设计早期确定。转换器看到的噪声量与其自己的噪声量之比即为SNR。SNR与带宽、信号质量(抖动)和增益相关。提高增益也会提高与之相关的噪声成分。

-

失真由无杂散动态范围(SFDR)来衡量,SFDR指rms满量程与峰值杂散频谱成分的rms值之比。

2. 输入架构类型

有两类ADC架构可供选择:缓冲型和无缓冲型。

缓冲架构的基本特征如下:

- 高线性度缓冲器,但需要更高的功率

- 更易设计输入网络与高阻抗缓冲器接口,因为它提供固定的输入端接电阻

- 缓冲器提供采样电容与输入网络之间的隔离,电荷注入瞬变更小

无缓冲架构的基本特征如下:

- 输入阻抗由开关电容设计设置

- 功耗较低

- 输入阻抗随时间变化(采样时钟 – 采样保持器)

- 来自采样电容的电荷注入反射回输入网络

3. 变压器耦合前端

一般说来,变压器耦合前端能够驱动较高中频而无显著损耗,具有更宽的带宽,功耗更低,并能提供固有的交流耦合。

4. 有源耦合前端网络

大多数有源耦合前端网络使用放大器。

针对交流和直流耦合应用选择放大器时,应考虑以下几点:

- 共模问题,工作电压低至1 VCM

- 电源问题(输入范围是多少?输出范围是多少?)

- 某些放大器只能用于交流耦合

- 输出端串联电阻使放大器保持稳定(5 Ω至10 Ω)

- 遵守数据手册中的布局布线指南:消除第二层上的地以保持低输出电流,并且避免振荡。

- 使用数据手册推荐的输出负载。有时候该负载值是一个固定电阻,而不是网络阻抗的乘积。

- 对于电流反馈放大器,务必阅读数据手册。数据手册给出了推荐的反馈电阻,该值决定放大器的稳定性。